随着科技的发展,System on Chip(SOC)已经成为电子设备的核心部件。从智能手机到汽车电子,SOC无处不在。然而,保证这些芯片在实际应用中的可靠性和性能,需要进行复杂而严格的测试。

SOC(System on Chip)是一种将CPU、内存、I/O接口等多种功能模块集成在单一芯片上的系统级超大规模集成电路。SOC测试则是确保这些集成电路在制造和实际应用中能够正常运行的重要步骤。它不仅包括数字电路的测试,还涵盖了模拟电路、存储器、功耗、电磁干扰等多个方面。

SOC测试通常分为以下几类:

1、数字电路测试:

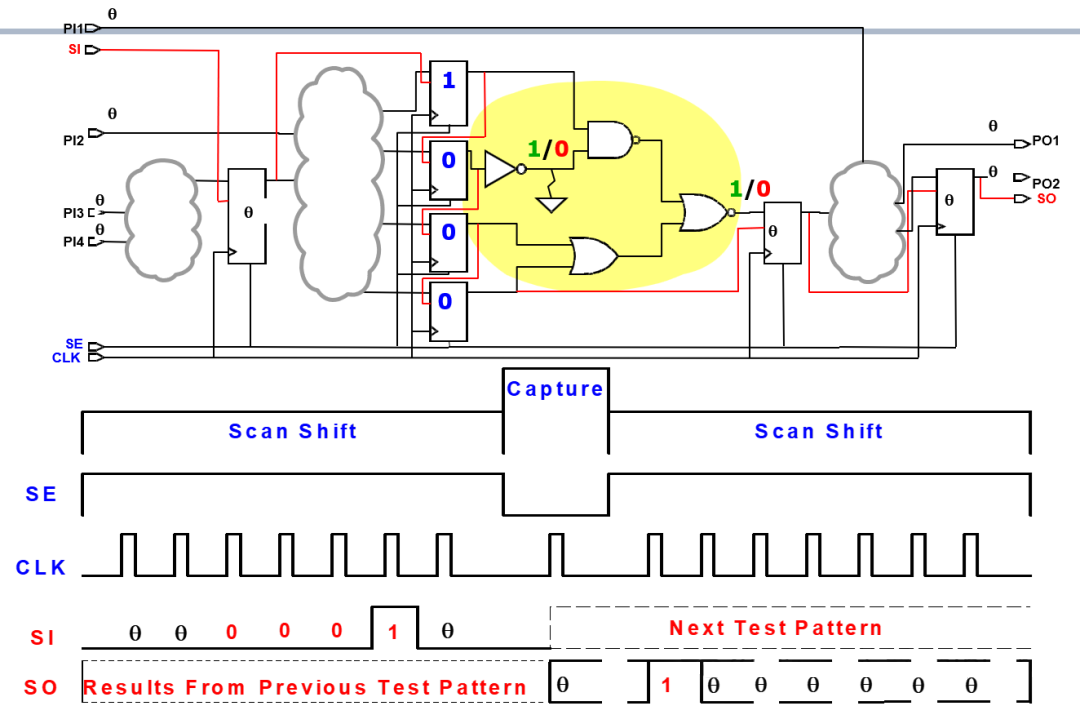

· 扫描测试(SCAN):通过扫描链将内部触发器转变为可观测的节点。

· 自动测试向量生成(ATPG):生成能够检测到电路中所有潜在故障的测试向量。

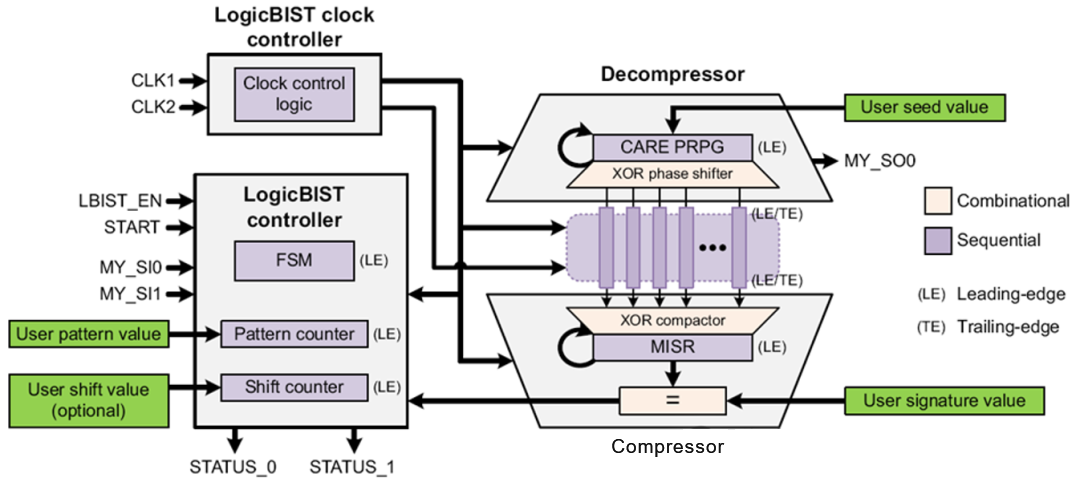

· 逻辑内建自测试(LBIST):利用内部生成的伪随机测试向量对逻辑电路进行自测试。

2、模拟电路测试:

· DC测试:检测直流参数如输入输出电压、电流。

· 模拟多路复用器(MUX)测试:对数模接口信号进行多路选择测试。

3、存储器测试:

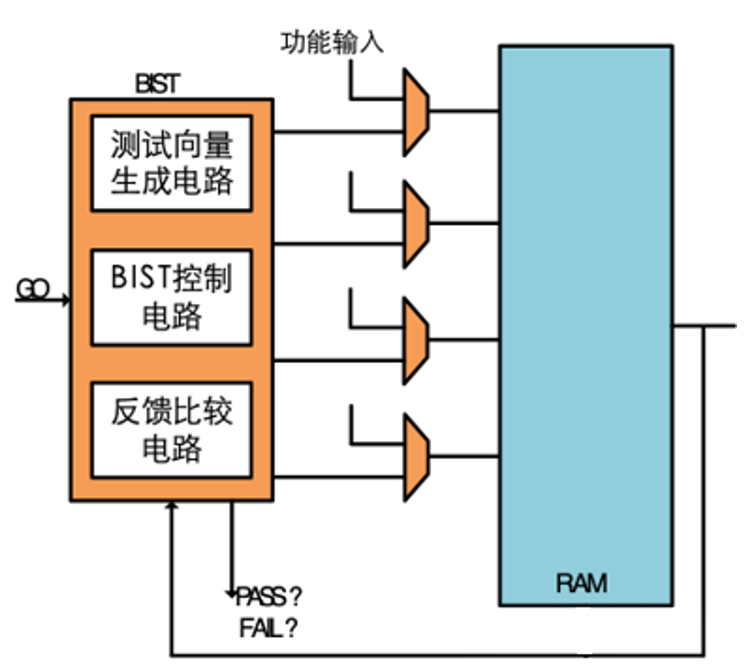

· 内建自测试(MBIST):对RAM、ROM等存储器的内部故障进行自测试。

· 存储器旁路模式测试:在基本扫描测试中使用旁路模式对存储器进行覆盖测试。

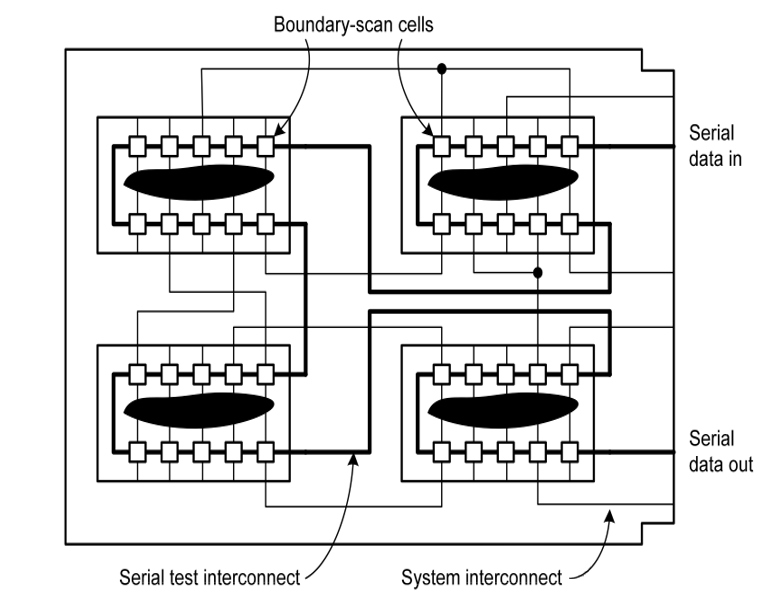

4、 IO测试:通过Boundary scan来测试IO

· JTAG协议:通过IEEE 1149标准,实现板级互连线测试和芯片内部IP调试。

· 边界扫描寄存器(BSR):在芯片的输入输出引脚上插入扫描寄存器,实现测试信号的可控和可观测。

5、功耗测试:

· 静态电流(IDDQ)测试:测量芯片在静态条件下的电流,以检测漏电流和短路故障。

· 低功耗模式测试:在不同低功耗模式下测量芯片的电流消耗。

6、电磁干扰测试:

· 静电放电(ESD)测试:通过人体放电模型(HBM)、机器放电模型(MM)等方法测试芯片对静电的耐受性。

SOC测试是保证芯片质量和性能的关键步骤。随着SOC集成度的提高,测试复杂性也显著增加,需要更多的测试向量和时间。测试成本占据芯片制造成本的很大比例,需要通过优化测试流程和技术降低成本。随着低功耗设计的普及,需要针对不同功耗模式进行测试,确保芯片在低功耗模式下的性能。随着科技的发展,SOC测试将不断进步,为芯片制造提供更加高效和可靠的保障。

本文章转载自网络,如有侵权请联系删除,谢谢!