等离子体蚀刻可能是半导体制造中最重要的工艺,也可能是仅次于光刻的所有晶圆厂操作中最复杂的。几乎一半的晶圆制造步骤都依赖于等离子体,一种高能电离气体来完成它们的工作。

为了可持续地制造出具有纳米级精度和正确结构的芯片,晶圆厂设备制造商需要突破等离子体物理、材料工程和数据科学的界限,提供所需的设备解决方案。这一点在等离子体蚀刻中最为明显,等离子体蚀刻与光刻技术携手合作,在晶圆上创造出精确、可重复的特征。

蚀刻工艺与光刻技术协同工作。蚀刻通常在沉积薄膜之前。通常,CVD薄膜涂有光刻胶,然后使用光学光刻通过图案化掩模版(掩模)曝光。抵抗发展然后揭示模式。在单晶片等离子体蚀刻室中,通常蚀刻化学物质和离子轰击并去除光致抗蚀剂缺失的CVD膜(在正色调抗蚀剂中)。蚀刻后,抗蚀剂灰化、湿式化学清洗和/或湿式蚀刻去除残留物。

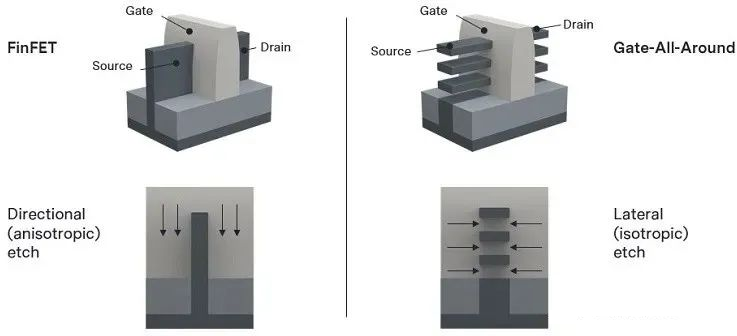

等离子体蚀刻工艺可以大致分为电介质、硅或导体蚀刻。二氧化硅和氮化硅等电介质最好使用氟化气体蚀刻,而硅和金属层与氯化学反应最好。基本上有三种干法蚀刻模式——反应离子蚀刻、等离子体蚀刻和溅射蚀刻(离子束)。蚀刻工艺都是关于化学反应物、等离子体和晶片材料之间的复杂相互作用。当RF偏压施加到反应性气体时,电子和带正电的离子轰击晶片以物理地去除(蚀刻)材料,而化学物质和自由基与暴露的材料反应以形成挥发性副产物。蚀刻可以是各向同性(垂直和水平反应相等)、各向异性(仅垂直)或介于两者之间。从finFET到GAA的转变驱动了关键的各向同性选择性蚀刻要求。

蚀刻工程师最关心的指标是蚀刻速率、轮廓控制、均匀性(整个晶片)和蚀刻选择性,因为这些都会影响产量和生产率。蚀刻选择性只是要蚀刻的材料相对于其底层的去除率,例如硅上的SiO2。在蚀刻期间,不去除过多的光致抗蚀剂也是有利的。但在这种情况下,通常在将图案转移到下面的膜之前,将其转移到硬掩模(二氧化硅、氮化硅、SiOC、TiN)。选择性规格从2:1到1000:1不等(高度选择性蚀刻)。随着每个新节点的出现,这些规范变得更加严格。随着高NA EUV在未来四年内开始取代常规EUV,焦点要低得多,所以不能再暴露厚的光刻胶,但仍然需要在下面对相同的膜厚度进行构图。

对于许多工具制造商来说,最棘手的步骤的蚀刻工艺优化可能需要一年或更长时间才能完成,工艺建模在蚀刻工艺开发中起着关键作用。能帮助工具制造商缩短上市时间,同时降低晶圆和掩模成本。

本文章转载自网络,如有侵权请联系删除,谢谢!